본문

Introduction

고속 전자 제품 설계 시 많은 어려움에 직면하게 됩니다. PCI-Express, DDRx, Serial ATA와 같은 고속 버스는 수백MHz에서 GHz 이상의 주파수로 동작하므로 timing margin이 빠듯합니다. 미세 형상 실리콘(Fine-geometry silicon)은 빠른 edge rate를 생성합니다.

그리고 더 작고 저렴한 제품에 대한 요구로 인해 PCB Layout의 배선 밀도는 점점 더 높아지고 있습니다. 고속 PCB design을 성공적으로 설계하기 위해선 이러한 모든 요소들이 고려되어야 합니다.

고속 design 제약 조건을 이용한 전자제품 설계 시, 세 가지 주요 영역(signal quality, timing, crosstalk)을 고려해야 합니다.

- Signal quality는 receiver를 손상시키거나 data error를 발생시키는 overshoot, ringback, non-monotonic 등과 같은 항목을 포함합니다.

- Termination, receiver loading, trace impedance, 길이의 영향을 포함한 timing은 system 레벨에서 준수를 보장하기 위해 PCB 레벨에서 엄격히 분석되어야 합니다.

- Crosstalk는 한 trace에 의해 다른 trace로 유기되는 원치 않은 noise로서, signal quality 및 timing 모두에 영향을 끼칠 수 있습니다.

이러한 영역을 분석하여 제품 신뢰성과 품질을 향상시킬 수 있습니다. 그리고 조건-결과(what-if) 시나리오를 테스트하여 routing 제약 조건을 만들고 layout에서 이를 검증하여 전기적인 요구 사항을 만족하는지 보장할 수 있습니다.

분석을 통해 trace 길이, topology, 간격, 부품 배치에 대해 합리적인 결정을 내릴 수 있고 board stackup, trace 폭, copper 중량과 같은 항목을 제한할 수 있습니다.

Signal Quality

Digital logic은 data를 일련의 1과 0으로 변환하며, 실제 시스템에서는 고/저전압으로 표현됩니다. Receiver가 전압이 1과 0중 어떤 값을 나타내는지를 결정하기 위해서는 전압이 receiver의 logic threshold보다 높거나 낮아야 합니다. 또한 이 전압은 receiver의 제한을 초과해서는 안되며 그렇지 않은 경우 손상될 수 있습니다. 이러한 두 가지 요구 사항은 신호 품질 분석에서 ringback 및 overshoot라는 두 가지 기본 제약 조건을 생성합니다.

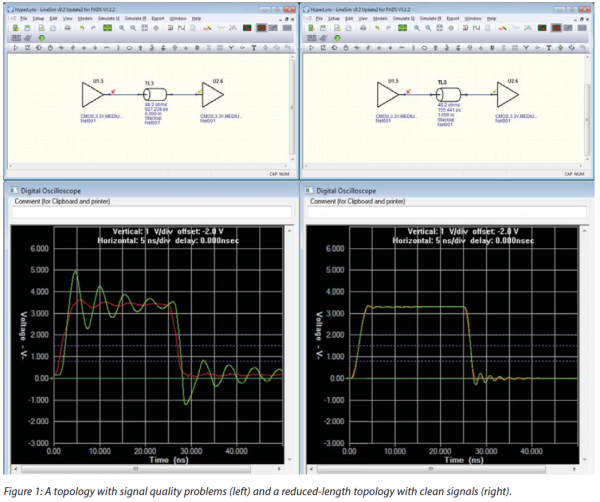

설계자 또는 엔지니어가 transmitter를 receiver에 그냥 연결한 경우엔 왼쪽의 그림 1과 같은 파형이 나옵니다. 여기서 우리는 ringback 및 overshoot 문제가 있는 것을 알 수 있습니다. 파형을 보면 1V를 초과하는 negative overshoot가 나타난 것을 확인할 수 있습니다. 또한 전압이 low logic threshold인 0.8V로 다시 올라가는 것(ring back)을 확인할 수 있습니다. 이 topology를 그대로 사용하여 PCB를 제작하면 data stream에서 오류가 발생하고 receiver가 손상될 수 있습니다.

Topology의 길이가 신호 edge의 길이보다 훨씬 아래로 줄어드는 경우 receiver에서의 파형이 극적으로 깨끗해집니다. 이것은 오른쪽에 있는 그림 1에서 볼 수 있습니다. 그러나 이러한 길이는 일반적으로 1인치 정도이므로 layout에서 항상 실현 가능하지는 않습니다.

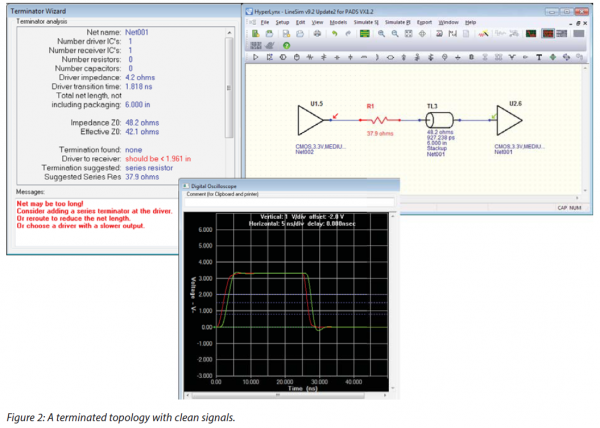

Receiver에서 신호를 깨끗하게 만드는 다른 방법은 termination을 사용하여 driver 및 receiver의 impedance를 board trace와 일치시키는 것입니다. 이를 통해 overshoot 및 ringback 문제를 발생시키는 reflection을 제어할 수 있습니다. 또한 trace의 길이가 비현실적인 최대 값으로 제한되지 않고 더 깨끗한 신호를 얻을 수 있기 때문에 Termination은 topology 길이에 대해 더 큰 유연성을 제공합니다.

Termination 값은 bus design guideline에서 얻거나 그러한 guideline이 없는 경우엔 분석을 통해 결정됩니다. PADS flow 내에 통합된 HyperLynx technology는 topology를 보고 이상적인 termination 값을 자동으로 결정할 수 있는 termination wizard를 통해 한 단계 더 나아갑니다.

Trace topology 내의 termination의 위치는 길이를 변경하고 결과를 분석하여 결정할 수도 있습니다.

Terminator의 위치를 결정하기 위한 maximum length rule은 이 분석을 통해 만들어지며 topology에서 다른 trace에 대한 길이 제한 조건도 마찬가지입니다.

이 예가 그림 2에 나와 있습니다. 이러한 모든 길이는 신호 품질 요구 사항을 충족시키는 가장 광범위한 solution space를 만들기 위해 분석될 수 있습니다.

▷ 원문보기 : Three Things to Consider When Designing Electronic Products with High-Speed Constraints

등록된 댓글이 없습니다.